### Semi-Automated Verification of Instruction Set Architectures

Georgy Lukyanov Dominique Devriese

June 16, 2020

Hardware (Assisted) Security

#### **Program Security**

#### Hardware (Assisted) Security

"Robust and compositional verification of object capability patterns." Swasey, Garg & Dreyer. 00PSLA'17. "Reasoning about object capabilities with logical relations and effect parametricity." Devriese, Birkedal & Piessens. EuroS&P'16.

"Linear Capabilities for Fully Abstract Compilation of Separation-Logic-Verified Code." Van Strydonck, Piessens & Devriese. *ICFP'19*. "Beyond good and evil: Formalizing the security guarantees of compartmentalizing compilation". Juglaret et al. CSF'16.

"Reasoning about a Machine with Local Capabilities." Skorstengaard et al, TOPLAS 42.1 (2019).

#### CHERI

"Rigorous engineering for hardware security: Formal modelling and proof [..]." Nienhuis et al. *IEEE S&P'20*.

#### PUMP

"Micro-policies: Formally verified, tag-based security monitors." De Amorim et al. *IEEE S&P'15*.

#### **Program Security**

#### Hardware (Assisted) Security

"Robust and compositional verification of object capability patterns." Swasey, Garg & Drever. 00PSLA'17. "Reasoning about object capabilities with logical relations and effect parametricity." Devriese, Birkedal & Piessens. EuroS&P'16.

"Linear Capabilities for Fully Abstract Compilation of Separation-Logic-Verified Code." Van Strydonck, Piessens & Devriese. *ICFP'19*. "Beyond good and evil: Formalizing the security guarantees of compartmentalizing compilation". Juglaret et al. CSF'16.

"Reasoning about a Machine with Local Capabilities." Skorstengaard et al, TOPLAS 42.1 (2019).

#### CHERI

"Rigorous engineering for hardware security: Formal modelling and proof [..]." Nienhuis et al. *IEEE S&P'20*.

#### PUMP

"Micro-policies: Formally verified, tag-based security monitors." De Amorim et al. *IEEE S&P'15*. Capability Safety for Capability Machines

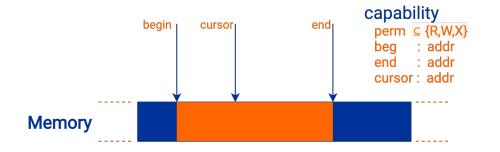

### **Capability Machines**

#### Hardware Guarantees

- Capabilities are unforgeable

- Permissions are checked

- Capability manipulation is safe

Can we verify this on the spec?

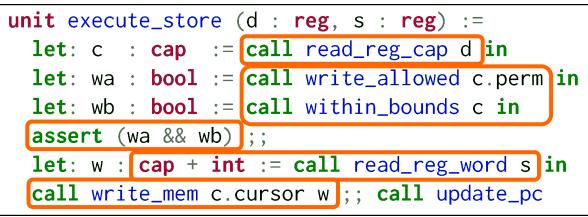

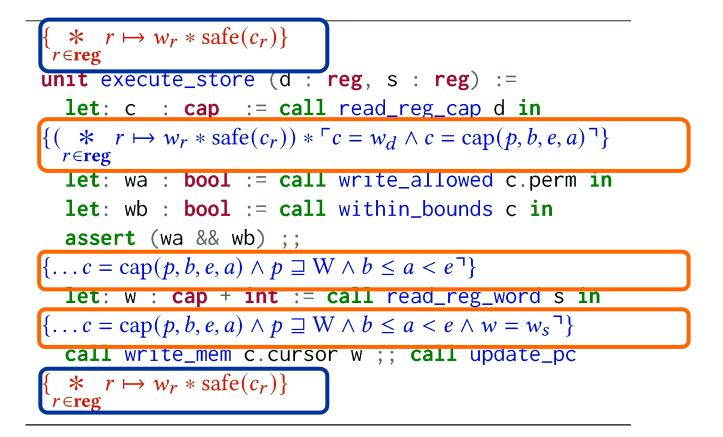

### **Example: Store Instruction**

µSail code for execute\_store

#### **Universal Contract**

#### Checks are critical!!

$$\{ \underset{r \in \mathbf{reg}}{\ast} r \mapsto w_r \ast \operatorname{safe}(w_r) \}$$

execute\_store d s

$$\{ \underset{r \in \mathbf{reg}}{\ast} r \mapsto w_r \ast \operatorname{safe}(w_r) \}$$

"Reasoning about a Machine with Local Capabilities." Skorstengaard et al, TOPLAS 42.1 (2019).

### **Universal Safety Contract**

#### Memory subset m

```

safe(cap(p,b,e,a))

⇔ [b,e[ ⊆ dom(m)

∧ (R ⊑ p =>

∀ a ∈ [b,e[. safe(m(a)))

∧ ...

```

$\{ safe(cap(p, b, e, -)) * safe(w) * \ulcorner b \le a < e \land p \sqsupseteq W \urcorner \}$ write\_mem a w  $\{ safe(cap(p, b, e, -)) * safe(w) \}$

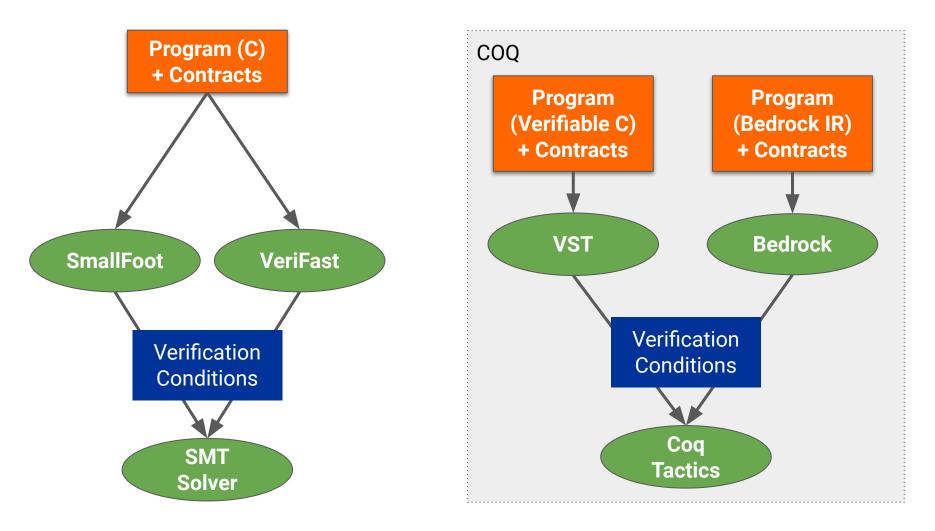

## Verifiers

### **Verified Verifiers**

Katamaran Verified Semi-Automated Separation Logic Verifier for Sail

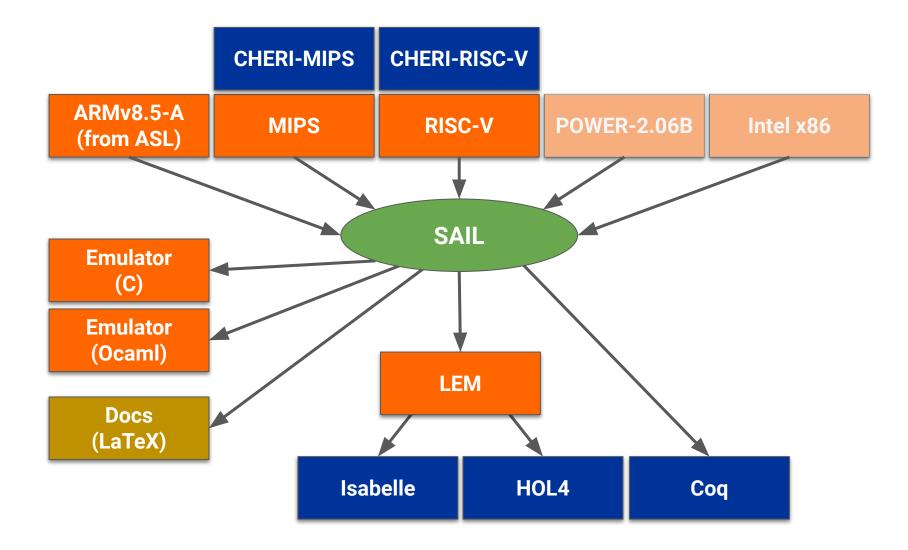

## Sail DSL for ISA Specifications

### Sail DSL for ISA Specifications

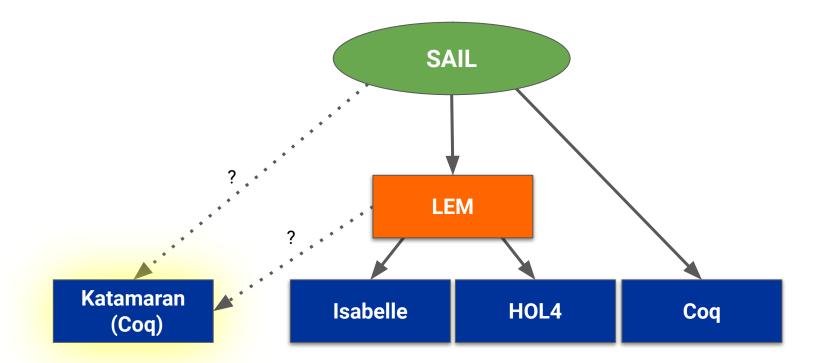

### Katamaran

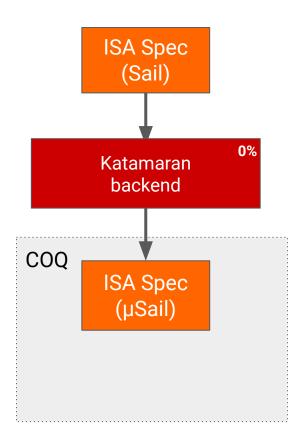

### Katamaran Workflow

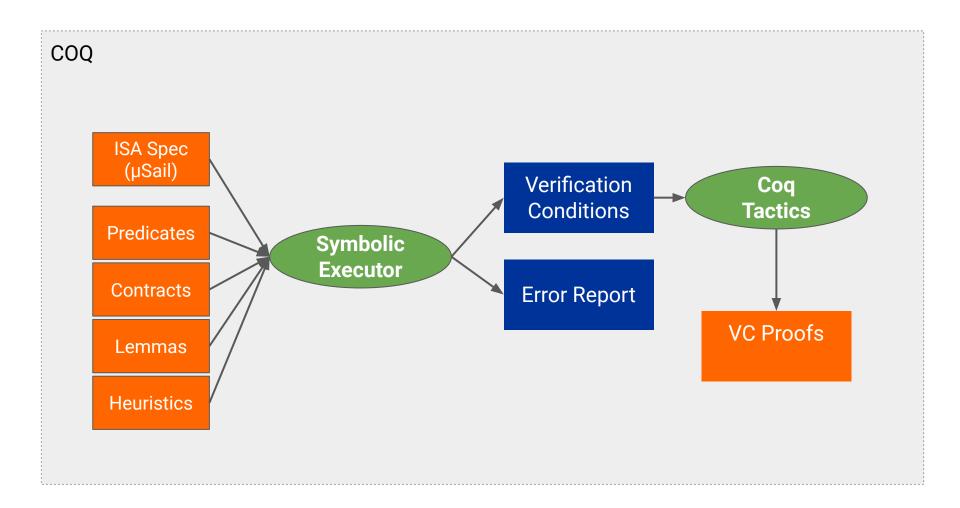

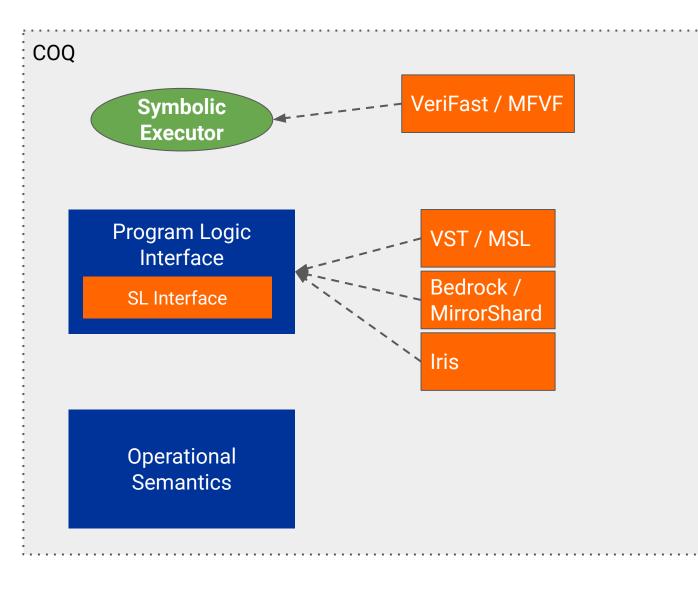

### Katamaran Structure

### Katamaran Structure

## µSail Language Features

| Mutable variables                             | Registers                                   | External functions |

|-----------------------------------------------|---------------------------------------------|--------------------|

| Primitive types<br>(Bool, enum, int, string,) | Structured types<br>(List, records, unions) | Type polymorphism  |

| Bitvectors Int/bool/order Return, exceptions, polymorphism while-loops |  |

|------------------------------------------------------------------------|--|

|------------------------------------------------------------------------|--|

| Scattered Definitions | Bidirectional mappings | Complex I-values |

|-----------------------|------------------------|------------------|

|                       |                        |                  |

Unsupported / Maybe planned

Not planned

# Sail Proof Support

- Shallow embedded syntax

- Monadic semantics (free prompt monad / state monad)

- Prover's assertion logic

- LTac / Eisbach

### Katamaran

- Deeply embedded syntax

- Operational semantics

- Embedded separation logic

- Gallina (reflective proofs)

# Future Work

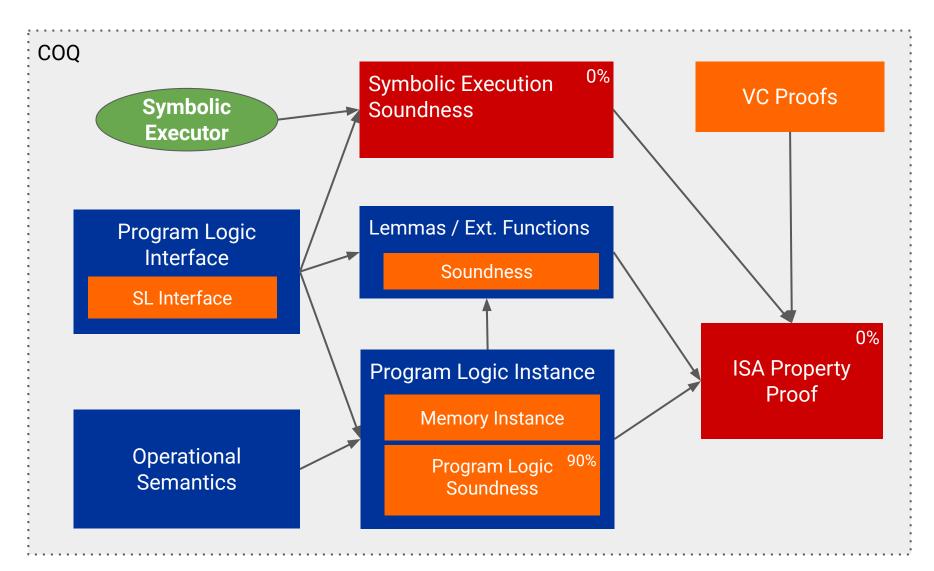

### Short Term Future

Program Logic Soundness

Symbolic Execution Soundness

Automation

Case Study: Register only capabilities

### Mid Term Future

### Program Logic Instance Iris?

#### Language Features Bitvectors

#### Linear capabilities

Skorstengaard, Devriese & Birkedal. "StkTokens: Enforcing well-bracketed control flow and stack encapsulation using linear capabilities." *POPL'19*. Local capabilities

Skorstengaard, Devriese & Birkedal. "Reasoning about a Machine with Local Capabilities." *TOPLAS* 42.1 (2019).

#### Uninitialized capabilities

Huyghebaert, Van Strydonck, Keuchel & Devriese. "Uninitialized Capabilities." *arXiv*:2006.01608 (2020).

REDFIN - REDuced instruction set for Fixed-point & INteger arithmetic

Mokhov, Lukyanov & Lechner. "Formal Verification of Spacecraft Control Programs." *Haskell'19*.

### Long Term Future

#### Sail Integration

#### CHERI

Woodruff et al. "The CHERI capability model: Revisiting RISC in an age of risk." ISCA'14.

#### Intel SGX

McKeen et al. "Innovative instructions and software model for isolated execution." HASP'13.

#### **Secure Compilation**

Patrignani, Ahmed & Clarke. "Formal approaches to secure compilation: A survey of fully abstract compilation and related work." *CSUR* 51.6 (2019).

# Thanks for your Attention!